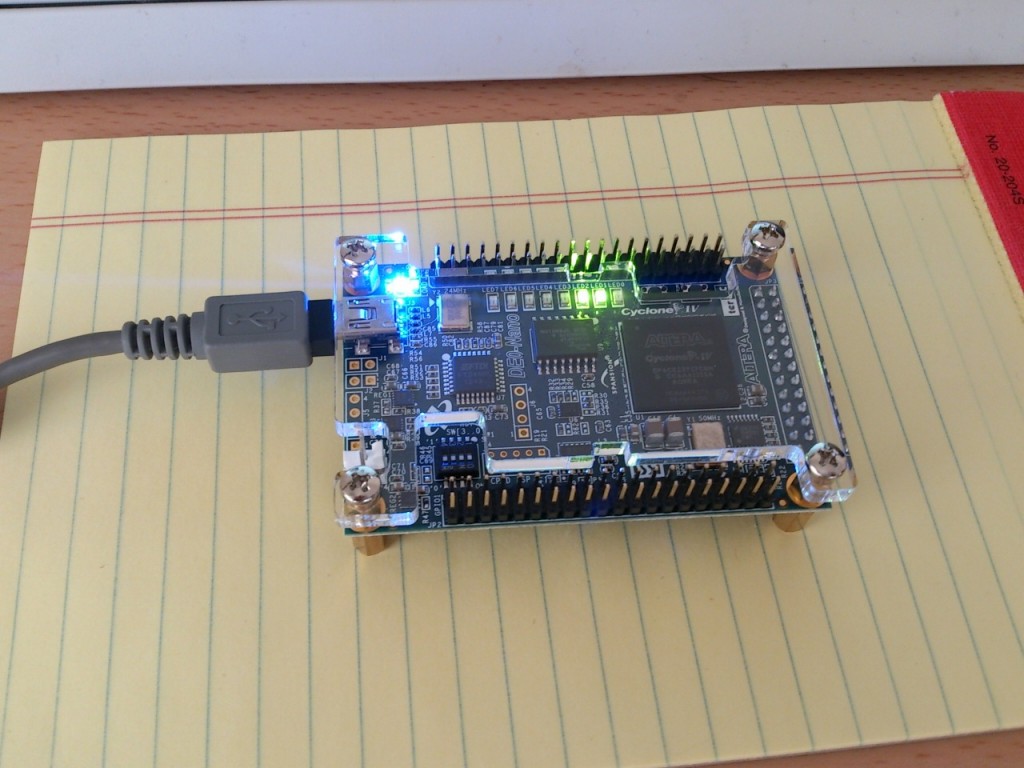

DEOCM (でおしむ) という MSX のスロットが付いたボードを家電のケンちゃんで買いました。DE0 と DE0-CV で使用可能のボードです。今回は古い DE0 に頑張ってもらうということで OneChipMSX на Altera DE0 – Development and Education Board のロシア語サイトのファームウエアを書き込んで使うことにしました。一応、DE0 というか Cyclone III は古いのでボードが余っている人向けの記事です。

今からやってみたい方は DE-CV(Cyclone V) + DEOCM-PLD-CV(仮称)計画 のファームウエアを使うといいでしょう。今回こちらの方法は記載していません。

ダウンロードするファイル

OneChipMSX на Altera DE0 の 2018年リリースのファイルをダウンロードします。

- source は 1chipMSX の DE0 版ソースです。コンパイルしてみたい人はダウンロード

- POF-file は DE0 のコンフィグレーションROM に書き込むコンパイル済みのファイルです。これは必要

- SOF-file は DE0 の FPGA に直接ダウンロードするアイルです。今回は使いません。

- BIOS MSXDOS2 SDHCカードに対応したMSX DOS2のROMファイル。MSXDOS2 の場合はこの .zip ファイル内の biossdhc.sys を使う。今回は使いません。

- BIOS NEXTOR SDカードに書き込むためのNextorシステム搭載のROMファイル。この .zip ファイル内の biosnext.sys は必要

OneChipMSX на Altera DE0 の 2017年リリースファイルのリンク

- NEXTOR メモリカードに書き込むシステムファイルのアーカイブ。アーカイブファイル これは必要

- OCM_NEXT.ROM – は、ディスクに書き込む最初のファイルでなければなりません。カードはFAT16形式でフォーマットされている必要があります。4Gバイト以上のSDHCカードをIBMカードフォーマットFAT32でフォーマットし、Nextor Basicに内蔵されているFDISKユーティリティで4Gバイトのパーティションに分割することをお勧めします。BASICからfdiskを呼び出す。これは不要

、NEXTOR という言葉が出てきました。DE0 版 MSX の DOS は Konamiman’s MSX page の DOS がターゲットです。

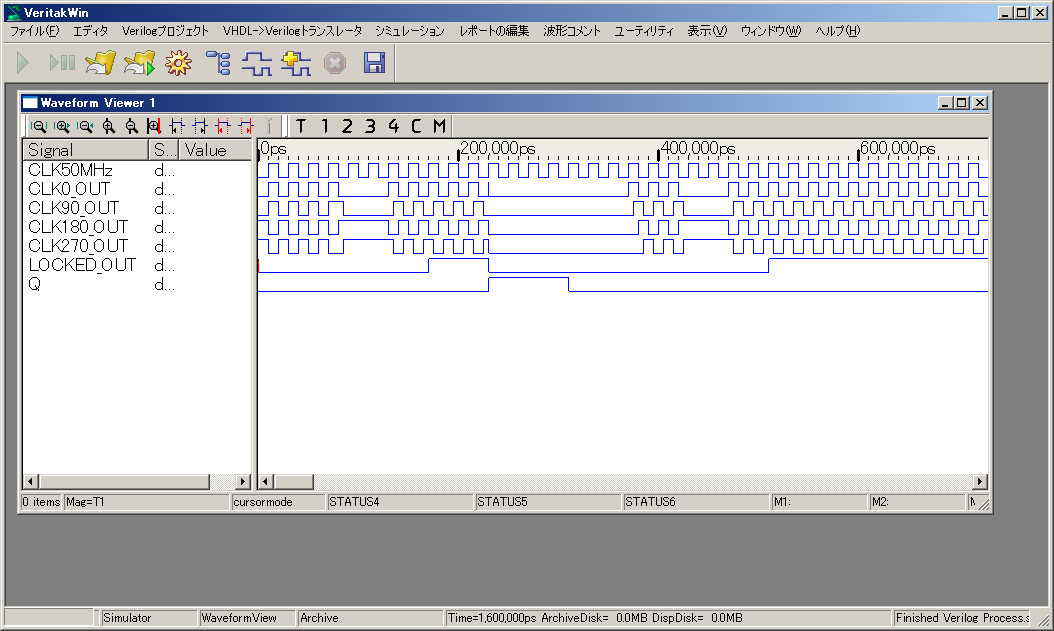

また、Intel FPGA サイトから Quartus II 13.1 もダウンロードしてインストールする。

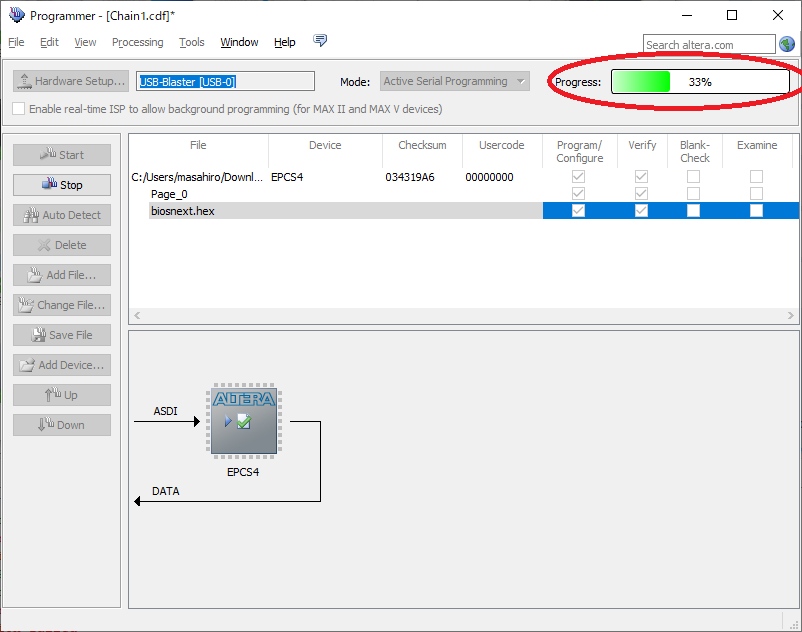

.pof ファイルの書き込み

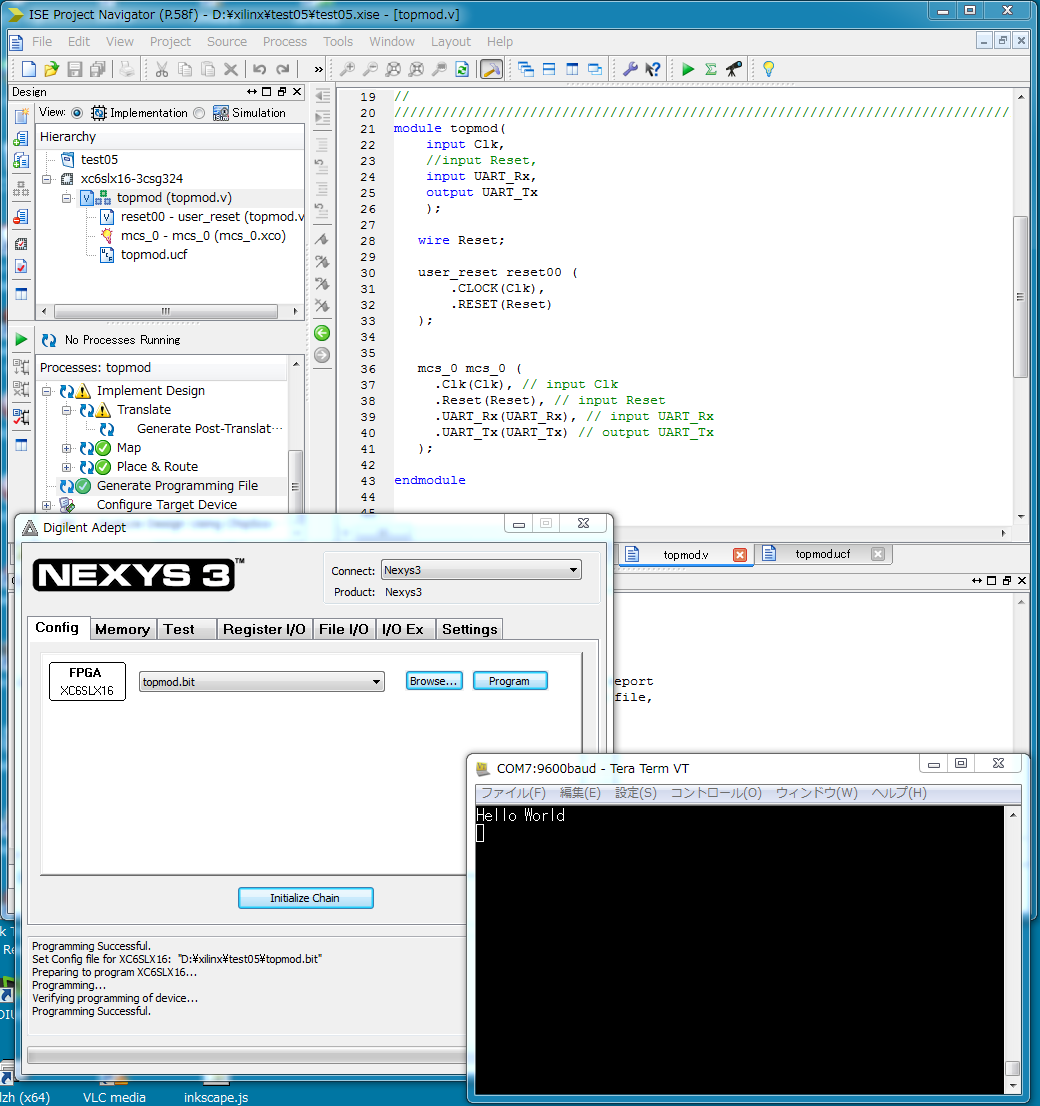

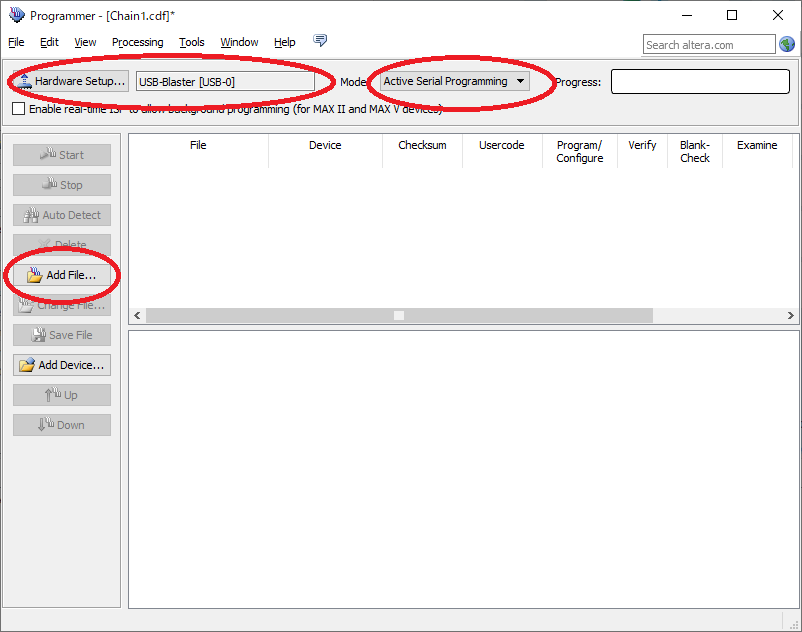

DE0 を PC と USB ケーブルで接続します。DE0 のスライドスイッチを PROG 側にしておきます。Quartus II 13.1 を起動して 「Tools」「Programmer」を選択してプログラマを起動します。

Hardware Setup で USB Blaster を選択。Mode は Active Serial Programming を選択する。

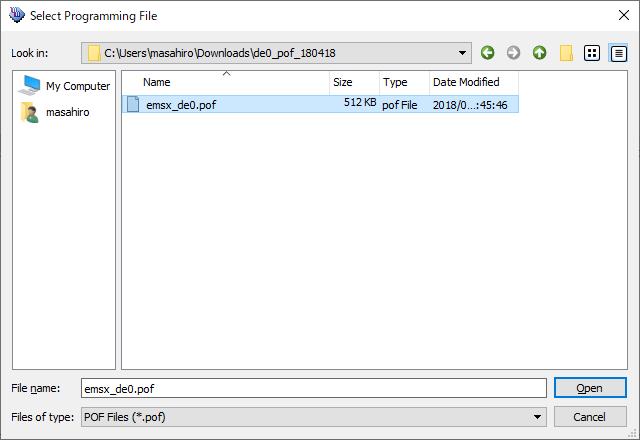

Add File ボタンを押してダウンロードした .pof ファイルを選択して Open ボタンを押す。

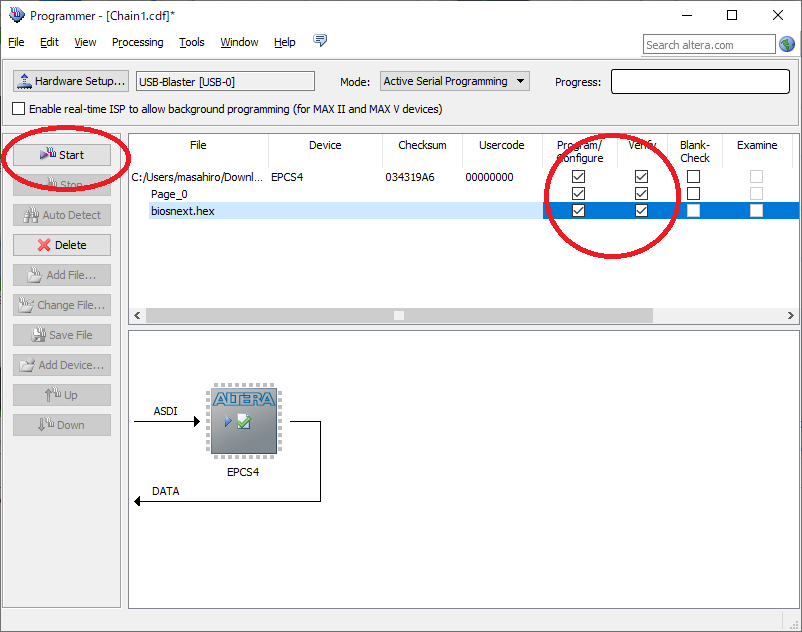

チェックボックスにチェックが付いた状態で Start ボタンを押す。

書き込みエラーになる場合は、スライドスイッチが PROG 側であること、また電源を入れ直して再度 Start ボタンを押せば故障でもない限り書き込み始まると思います。書き込みが終了したら、電源を切ってスライドスイッチを RUN に戻してください。

MSXDOS の SD(microSD)カード作成

NEXTOR DOS を microSDカードに書き込みします。コマンドプロンプトを起動して、DISKPART コマンドを起動します。管理者モードの確認ダイアログが出たら OK で続行。そうすると、もう一枚コマンドプロントのウィンドウが表示され DISKPART> のプロンプトが表示されます。

まず、microSD カード内の不要パーティションを削除します。下記は Raspberry Pi で使用した microSD カードでしたので、boot のパーティションと ext4 のパーティション2つあるやつでした。下記実行例のようにパーティション削除を行います。

DISKPART> LIST DISK

ディスク 状態 サイズ 空き ダイナ GPT

### ミック

------------ ------------- ------- ------- --- ---

ディスク 0 オンライン 931 GB 2048 KB *

ディスク 1 オンライン 931 GB 0 B *

ディスク 2 オンライン 1863 GB 0 B

ディスク 3 メディアなし 0 B 0 B

ディスク 4 オンライン 14 GB 3072 KB

DISKPART> SELECT DISK 4

ディスク 4 が選択されました。

DISKPART> LIST PARTITION

Partition ### Type Size Offset

------------- ------------------ ------- -------

Partition 1 プライマリ 41 MB 4096 KB

Partition 2 プライマリ 14 GB 46 MB

DISKPART> SELECT PARTITION 2

パーティション 2 が選択されました。

DISKPART> DELETE PARTITION

DiskPart は選択されたパーティションを正常に削除しました。

DISKPART> SELECT PARTITION 1

パーティション 1 が選択されました。

DISKPART> DELETE PARTITION

DiskPart は選択されたパーティションを正常に削除しました。

DISKPART> LIST PARTITION

このディスクには表示するパーティションがありません。

DISKPART>これで、microSD にパーティションが無い状態になりました。また、SELECT DISK をした後に CLEAN コマンド一発でパーティションをすべて削除できます。SELECT DISK を間違えると大変なことになるので、好きな方法で microSD カードの中身を削除してください。

DISKPART> help clean

フォーカスされたディスクからすべてのパーティション フォーマットまたは

ボリューム フォーマットを削除します。

構文: CLEAN [ALL]

ALL ディスク上のすべてのバイトおよびセクターをゼロに設定するように指定します。

これにより、そのディスクに格納されているすべてのデータが完全に削除されます。

マスター ブート レコード (MBR) ディスクでは、MBR パーティション情報と

隠しセクター情報だけが上書きされます。GUID パーティション テーブル

(GPT) ディスクでは、プロテクティブ MBR を含む GPT パーティション情報が

上書きされます。ALL パラメーターを使用しない場合、最初の 1 MB と最後の

1 MB がゼロに設定されます。これにより、以前にディスクに適用された

フォーマットは消去されます。ディスクの消去の後、ディスクの状態は

未初期化になります。

例:

CLEAN

パーティションを作成する。

DISKPART> CREATE PARTITION PRIMARY SIZE=2000

DiskPart は指定したパーティションの作成に成功しました。

DISKPART> ACTIVE

DiskPart は現在のパーティションをアクティブとしてマークしました。

DISKPART> FORMAT FS=FAT QUICK

100% 完了しました

DiskPart は、ボリュームのフォーマットを完了しました。

DISKPART> SET ID=06

DiskPart は、パーティション ID を設定しました。

DISKPART> DETAIL PARTITION

パーティション 1

種類 : 06

隠し属性 : いいえ

アクティブ : はい

オフセット (バイト): 1048576

Volume ### Ltr Label Fs Type Size Status Info

---------- --- ----------- ---- ---------- ------- --------- --------

* Volume 8 I FAT リムーバブル 2000 MB 正常

DISKPART>Ltr は ドライブレターなので、パソコンによって変化します。DISKPART のコマンドプロンプトウィンドウを閉じます。

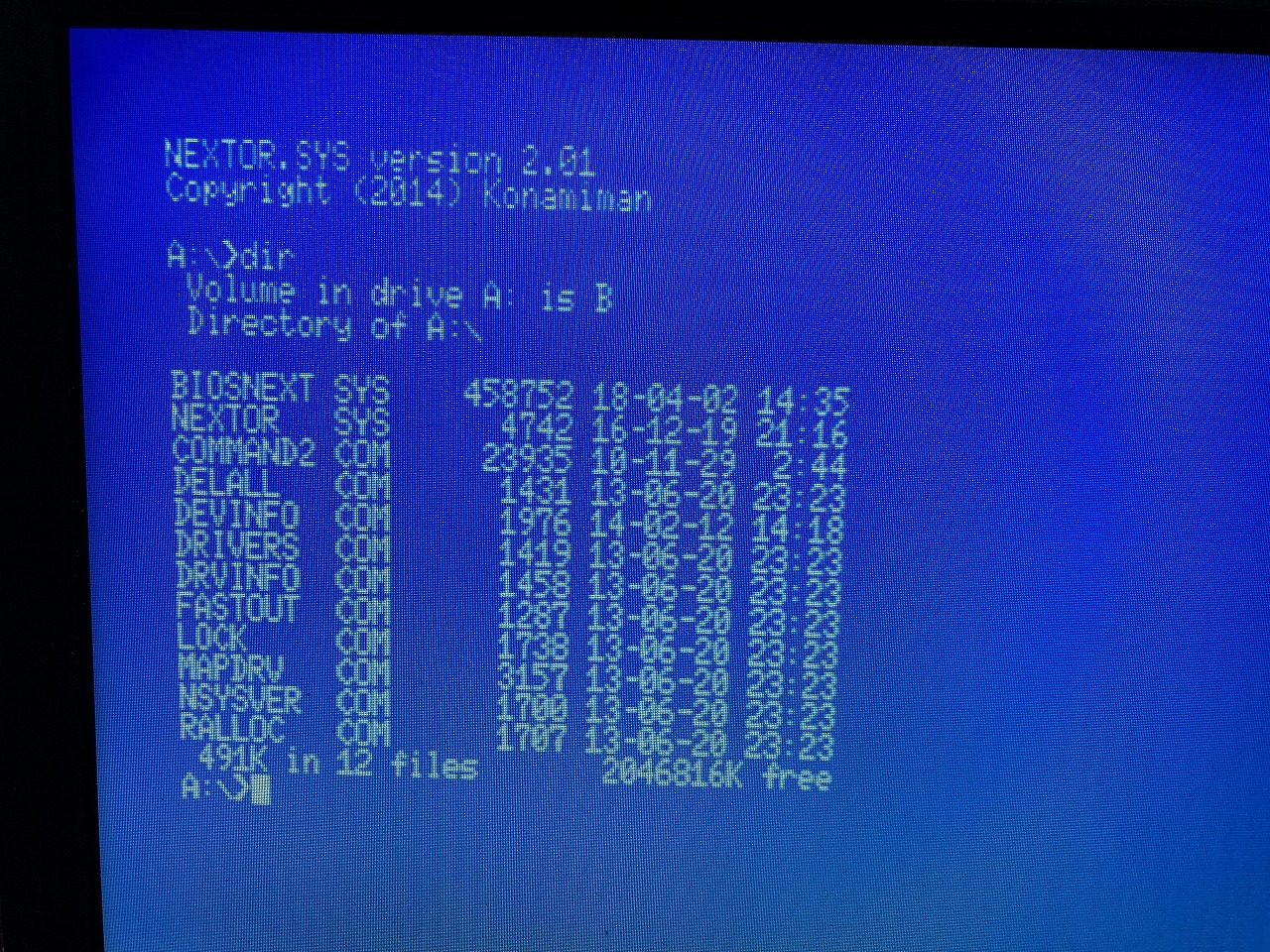

microSD カードに、NEXTOR DOS のファイルをコピーします。ロシア語サイトからダウンロードした biosnext.zip と nextor.zip を解凍しておきます。そして、biosnext.zip ファイル内の biosnext.sys を最初に microSD にコピーします。nextor.zip は NEXTOR.SYS と *.COM ファイルをコピーします。これで microSD カードから起動できます。

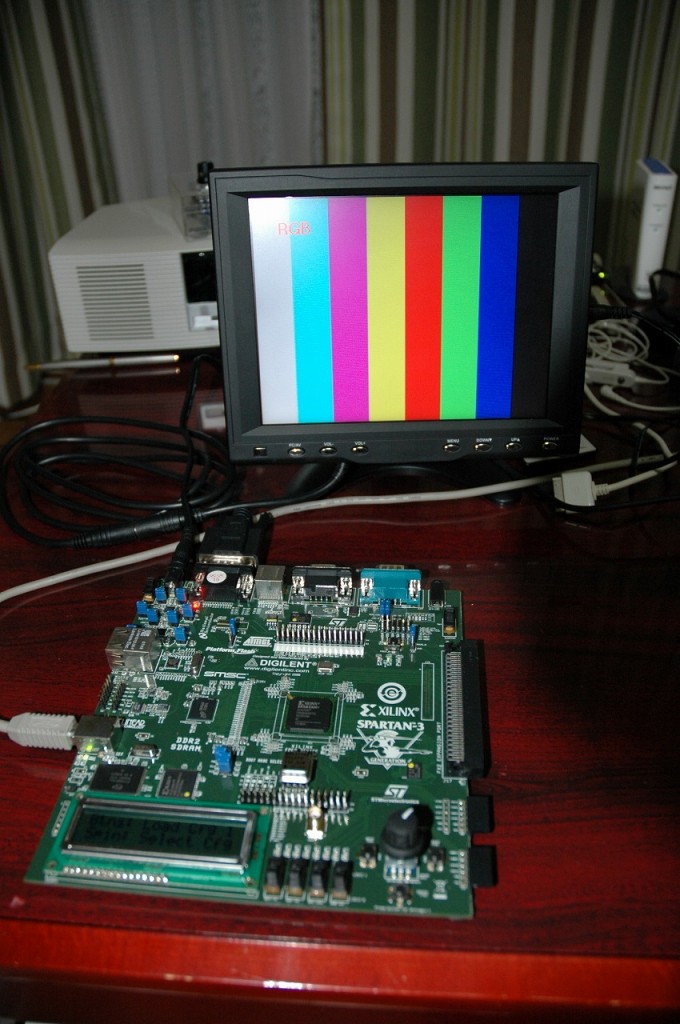

MSXDOS 起動

microSDカードを取り外して、DE0の SDカードスロットに装着します。大きさ変換のアダプタを使用して差し込みます。また、VGA 液晶、PS/2 キーボードも接続します。10個並んだスライドスイッチは全部 OFF で電源を入れます。

Initial Program Loader のメッセージやロゴが表示された後、MSXDOS のプロンプトが表示されれば成功です。

NEXTOR.SYS verstion 2.01 と表示されて konamiman dos が起動しています。

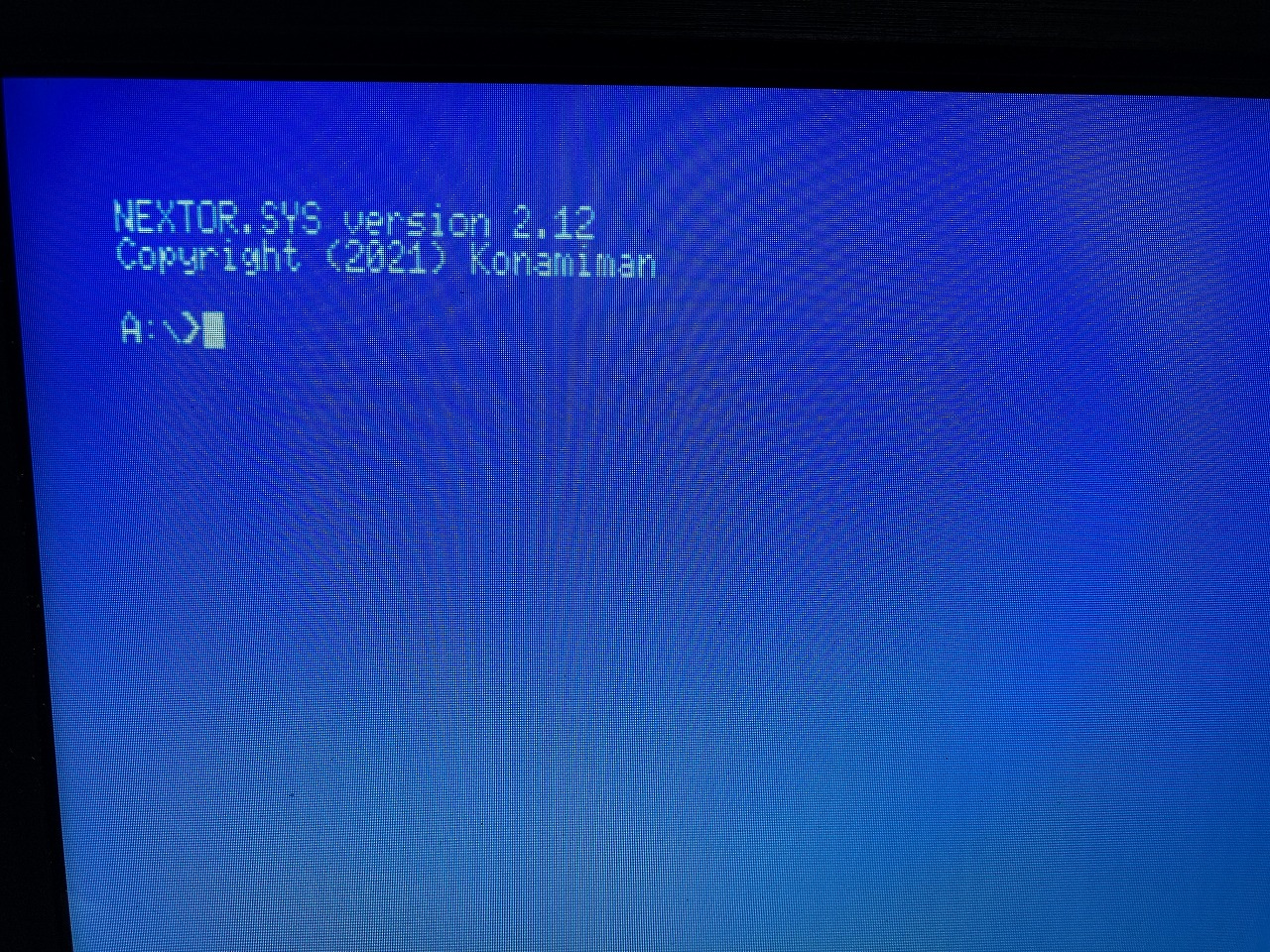

https://github.com/Konamiman/Nextor/releases

の最新リリースにある NEXTOR.SYS.japanese をNEXTOR.SYS にリネームし、microSDカードに上書きしてところ version 2.12 と表示され起動しましたので、その他コマンド類もリポジトリの最新版を build して置き換えてもいいと思われます。

あとは、Louthrax’s MSX game room から、sofarun をダウンロードして microSD にいれておけば、 .dsk のディスクイメージもファイルを選んでボタンクリックするだけで起動してくれる便利なソフトなので導入しておきましょう。