この土日は散歩しに行こうと思いつつも、土曜日の朝、「積み基板で遊ぼう」と思いついたのが優先事項になってしまいまして NEXYS3 SPARTAN-6 LX16 ボードをひっぱり出す。Xilinx のサイトにある、XAPP495(Implementing a TMDS Video Interface in the Spartan-6 FPGA) をダウンロードして作業開始。

この XAPP495 の対象ボードは Digilent の ATLYS という SPARTAN-6 LX45 搭載のボードが対象です。私の積み基板のより規模の大きいのが載ってまして HDMI コネクタもオンボードで付いてます。私のには HDMI コネクタが付いていないので、この NEXYS 3 基板買ったときに追加の小さいボードも買いました。これにマイクロなHDMI コネクタが4つとpmodコネクタ3つ付いてます。

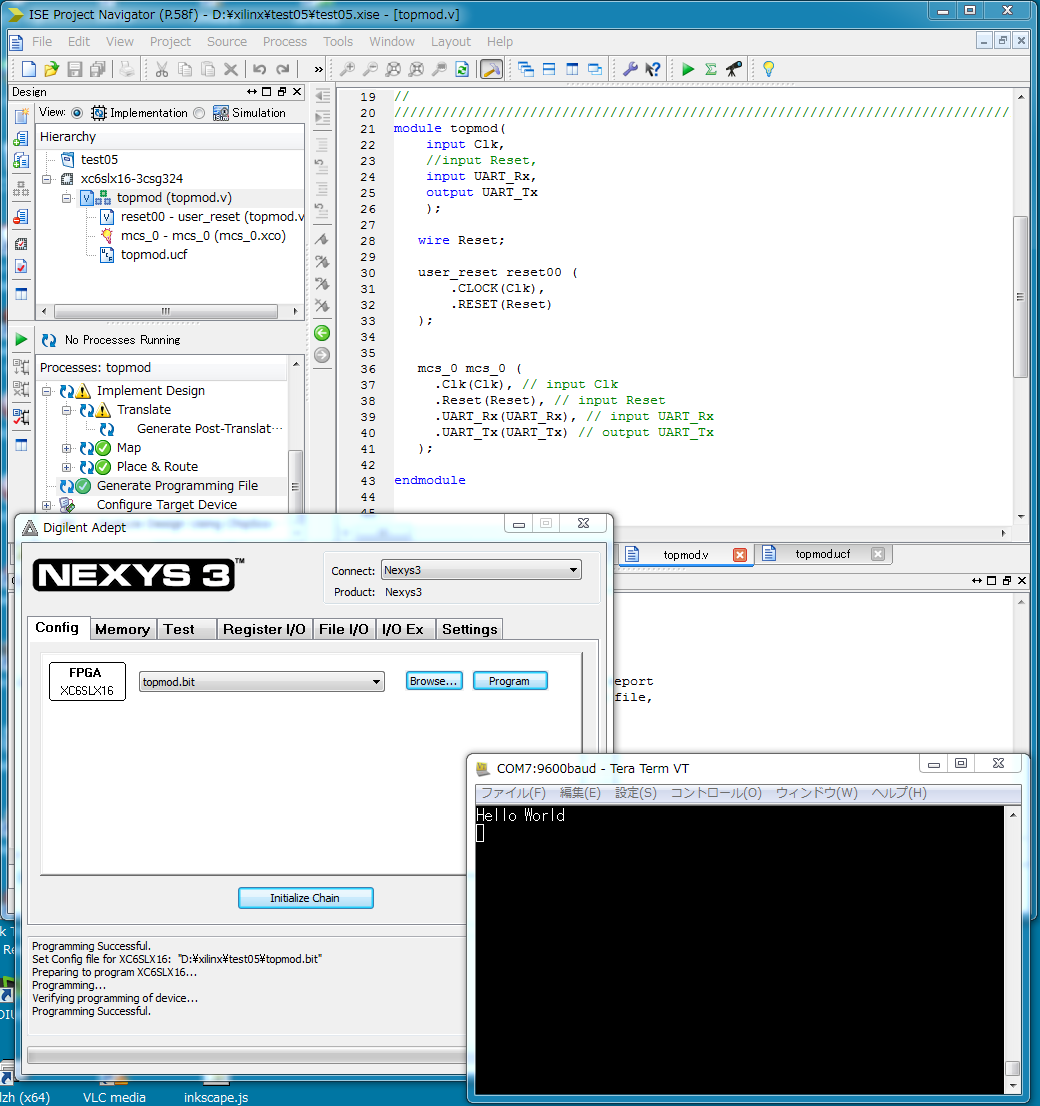

今回はカラーバー出れば満足なので、Planahead 14.7 で新規プロジェクトを作成しサンプルのソースから vtc_demo.v をトップモジュールにして ucf ファイル書き換えてシンセサイズとインプリして、書き込みしたら OK なはずでした。

が、ioclock が配線出来ませんと言われ土曜日の午前中はあきらめて一旦終了。

こういうときは UCF ファイルが悪いのが相場なので、オリジナル ATLYS 基板用の UCF でビルドしてワーニングとかは出るもののインプリメント出来るのを確認。結局のところ 100MHz のクロック入力が、 ATLYS は BANK1 のポート、NEXYS3 は BANK2 のポートですが、この UCF のピン番号を替えたらエラーの山でした。

モジュールの内部は 50MHz で動いているので、100MHz のクロックを50MHz にしているところがあります。ここらへんを書き換えたら動くのではないかと修正開始。

IBUF sysclk_buf (.I(SYS_CLK), .O(sysclk));

BUFIO2 #(.DIVIDE_BYPASS("FALSE"), .DIVIDE(2))

sysclk_div (.DIVCLK(clk50m), .IOCLK(), .SERDESSTROBE(), .I(sysclk));

BUFG clk50m_bufgbufg (.I(clk50m), .O(clk50m_bufg));

もとのソースは クロック入力ピンを IBUF で受けて、それを BUFIO2 で分周。50MHz 出力を BUFG でグローバルなクロック配線に載せるいうことをやっています。これの入力のピン位置がかわるだけで、インプリ出来んのはバグちゃう?と思いたくなりますが、仕方ありません。

- DCM で 50MHZ を作ってそれを使うように修正してみたところ、「タイミング守れません」でアウト。FPGA EDITOR でDCM変更でなとかなるかもしれませんが、なんとかするスキルはありません(笑)

- 仕方ないので always で分周する方法を。遅延なしにちゃんと分周出来る保証はありませんが簡単なのでやってみたら動きだした

という次第。居間にあるハーフパネルの液晶テレビ(家に HDMI 入力あるのはこれだけで PC は DVI なので変換が必要)に接続してみて、表示されるか確認。「信号がありません」とは言われませんでした。表示サイズがあわないかしておかしい表示になっていますが一つ進んだかな。