Terasic の DE0-Nano ボードで、メモリマップド I/O のテストを PC 側のコンソールから出来るらしいので試してみます。

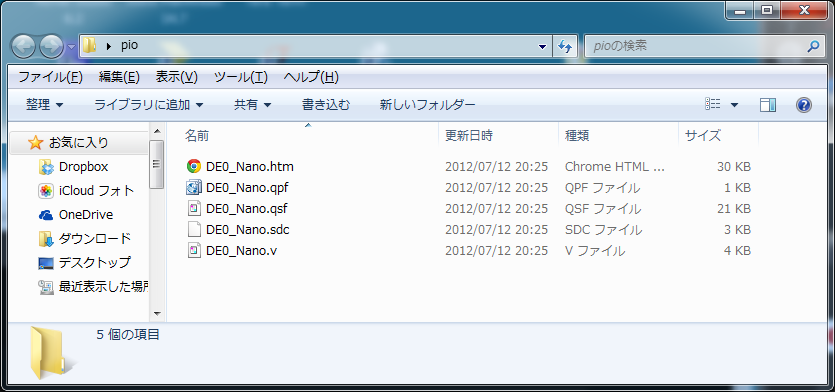

DE0-Nano ボード付属 CD にあるサンプルプロジェクト DE0_Nano_GOLDEN_TOP フォルダをコピー・ペーストして作業用フォルダを作成します。DE0_Nano.qpf をダブルクリックして、Quartus II を立ち上げます。

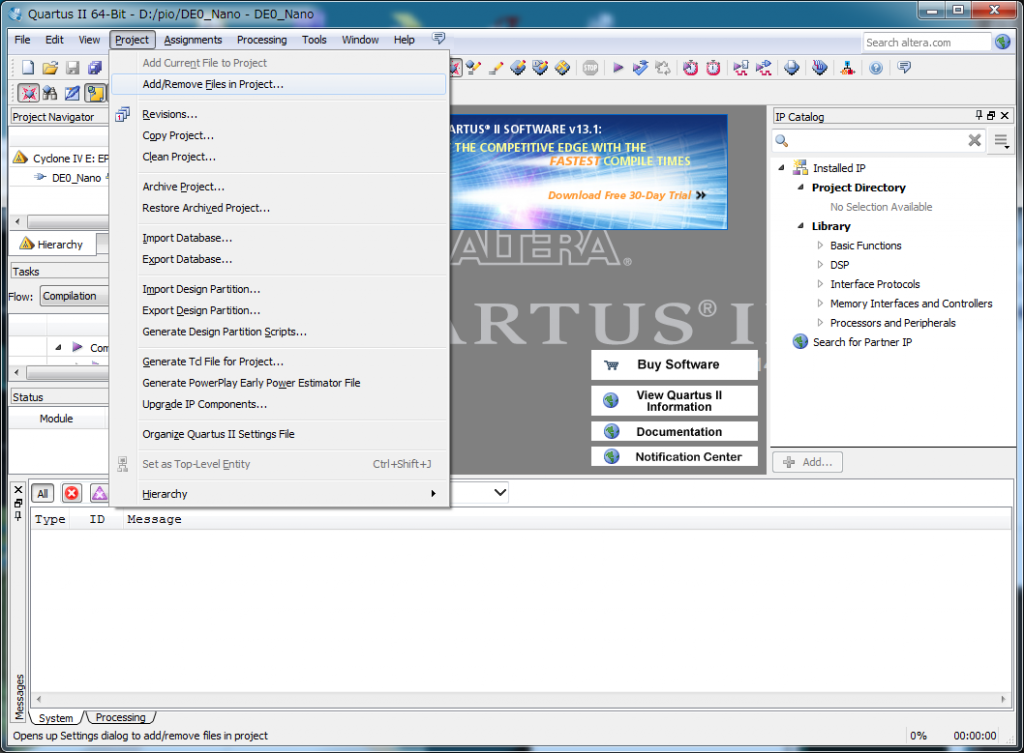

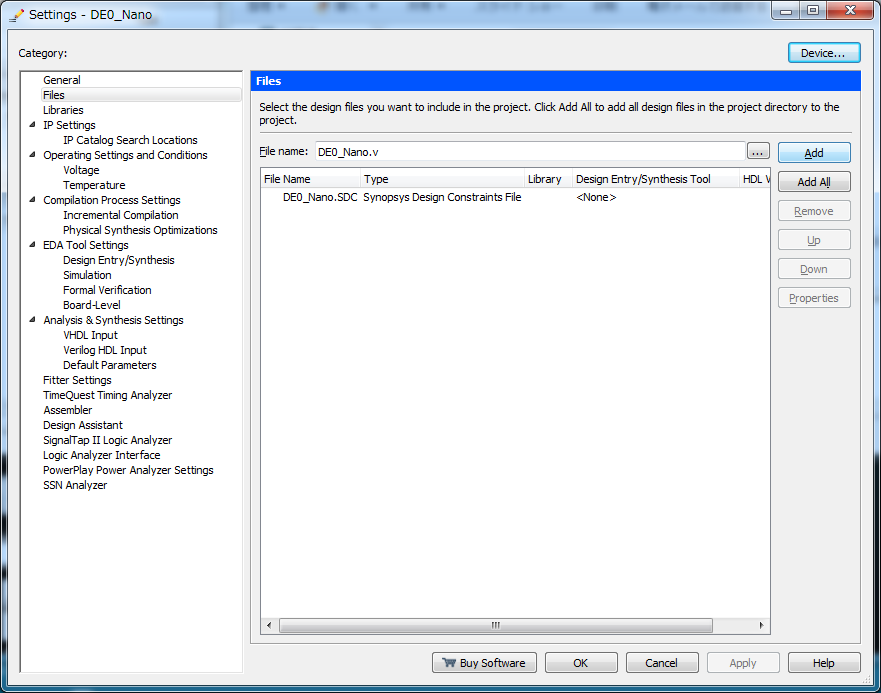

プロジェクトに作業フォルダ内の DE0_Nano.v ファイルを追加します。

Project メニューから Add/Remove Files in Project でファイル追加を行います。

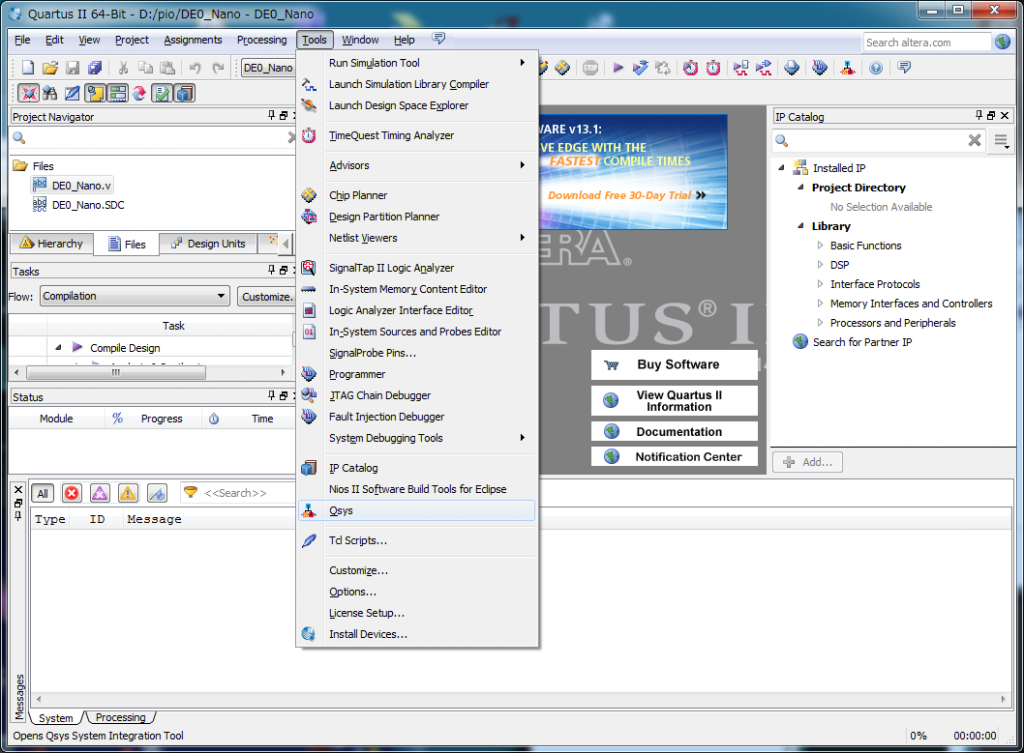

Qsys を起動します。

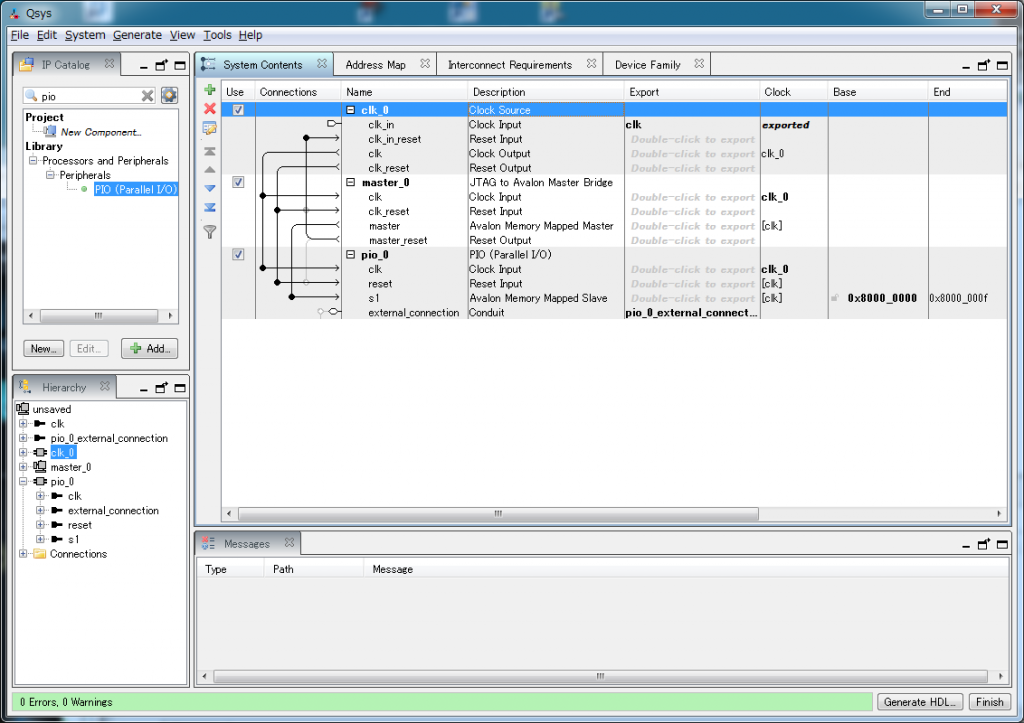

Qsys を起動して、JTAG to Avalon Master Bridge と PIO (Parallel I/O) を追加します。

JTAG to Avalon Master Bridge 追加時の設定変更なし

PIO (Parallel I/O) 追加時の設定変更なし(Direction が Output でなければ Output にする)

各コンポーネントの配線は、画面コピー参照

Export 名の設定は、PIO の出力を、FPGA のポートに付けないといけないので PIO external_connection 行にある export 欄をダブルクリックして export します。今回は名前変更せずそのまま使用しています。

PIO の S1 のメモリマップ上のアドレスを入れます。今回は試しに 0x8000_0000 にしました。アドレスのところをクリックして修正します。

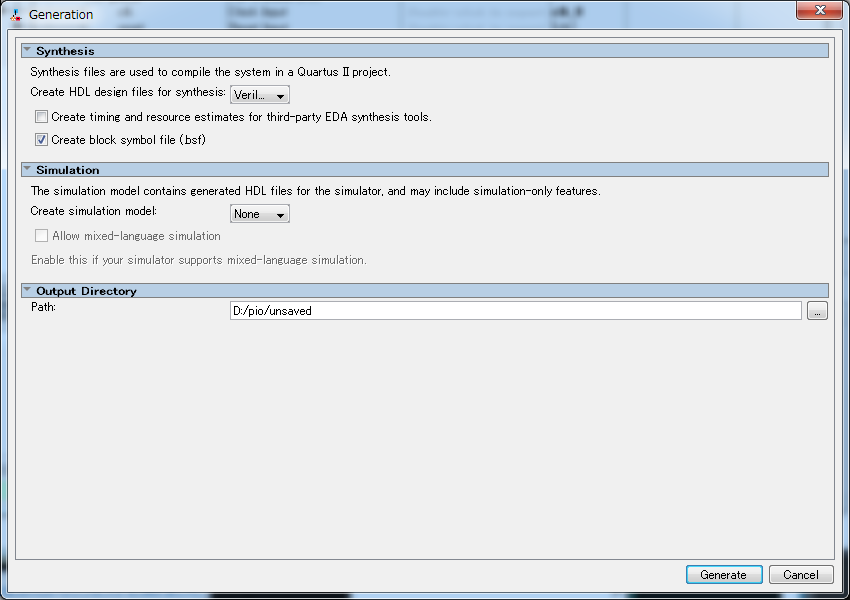

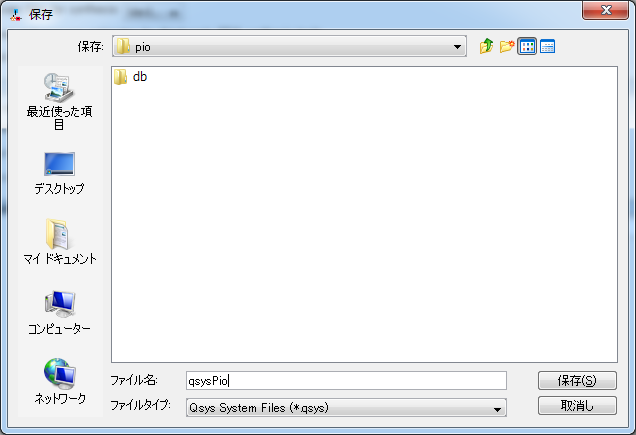

設定が終れば、Generate -> Generate HDL を選択して Qsys の HDL を生成します。Generate ボタンを押すと処理開始ですが、作成した設定を保存していないので、セーブのダイアログが出ます。今回は qsysPio という名前で保存しました。

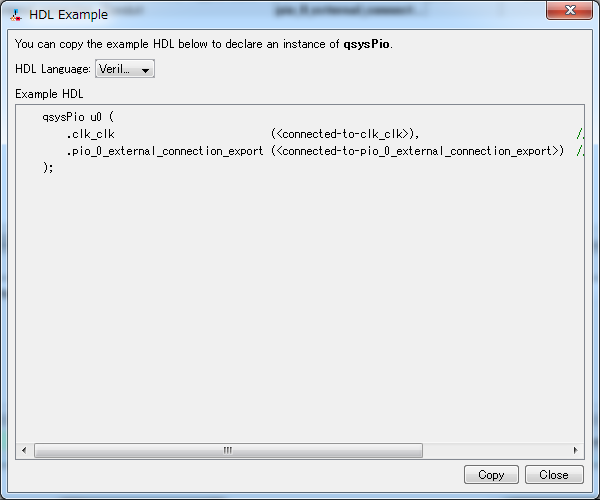

Qsys の Generate が完了したら、 DE0_Nano.v に Qsys のインスタンス作成するためのコードを書かないといけません。 Generate -> HDL Example を選択して インスタンスするコードをクリップボードにコピーします。そして DE0_Nano.v を開いてペーストします。

qsysPio u0 (

.clk_clk (CLOCK_50), // clk.clk

.pio_0_external_connection_export (LED) // pio_0_external_connection.export

);

endmodule

ファイルの最後に endmodule がありますが、その手前にペーストして、() 括弧の中を書き換えます。

クロック入力は、CLOCK_50 、LED 出力は LED という名前です。修正が終れば CTRL-S で上書き保存。

次に Qsys の Generate 時に保存した、qsysPio.qsys をプロジェクトに追加します。 DE0_Nano.v を追加したときと同じ手順で追加します。

Processing -> Start Compilation や、コンパイルボタンを押してコンパイルします。

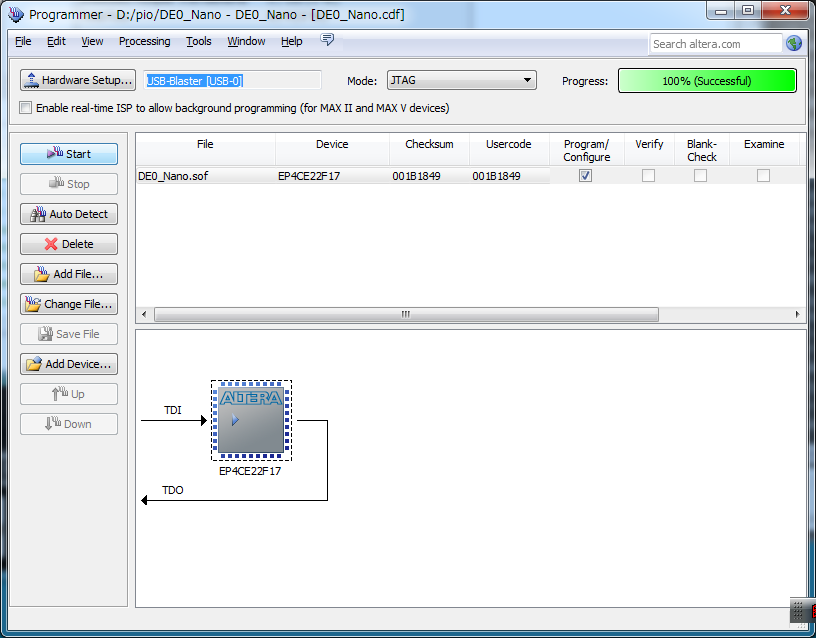

コンパイル完了したらプログラマで DE0-Nano ボードへ .sof ファイルを書き込みます

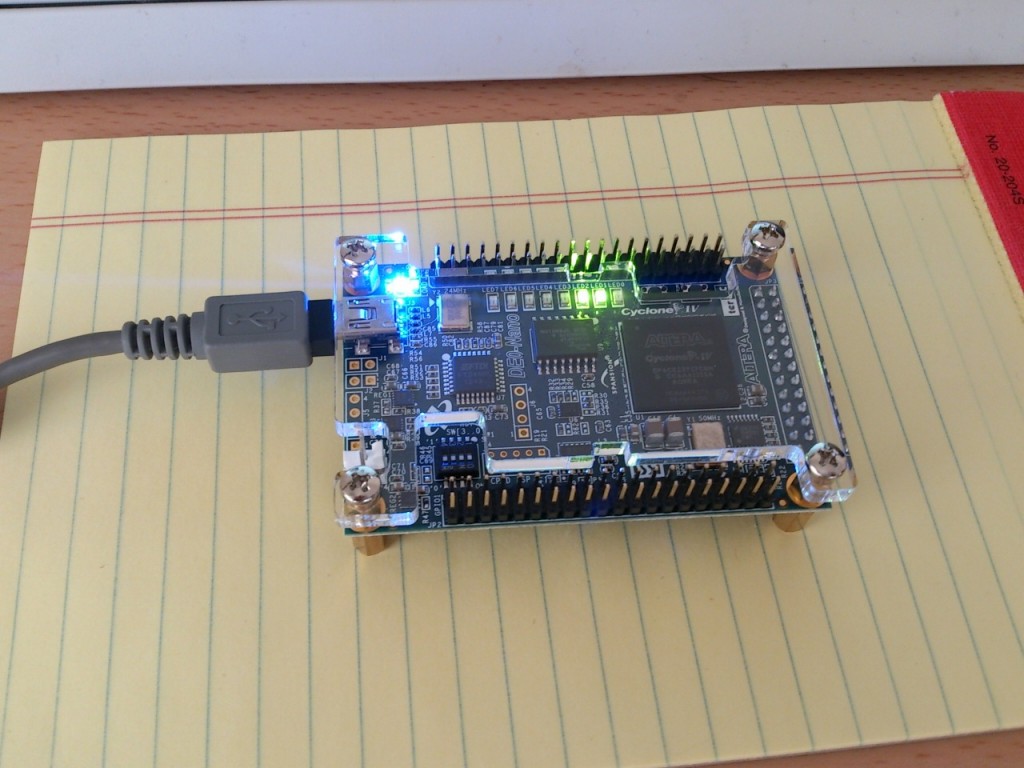

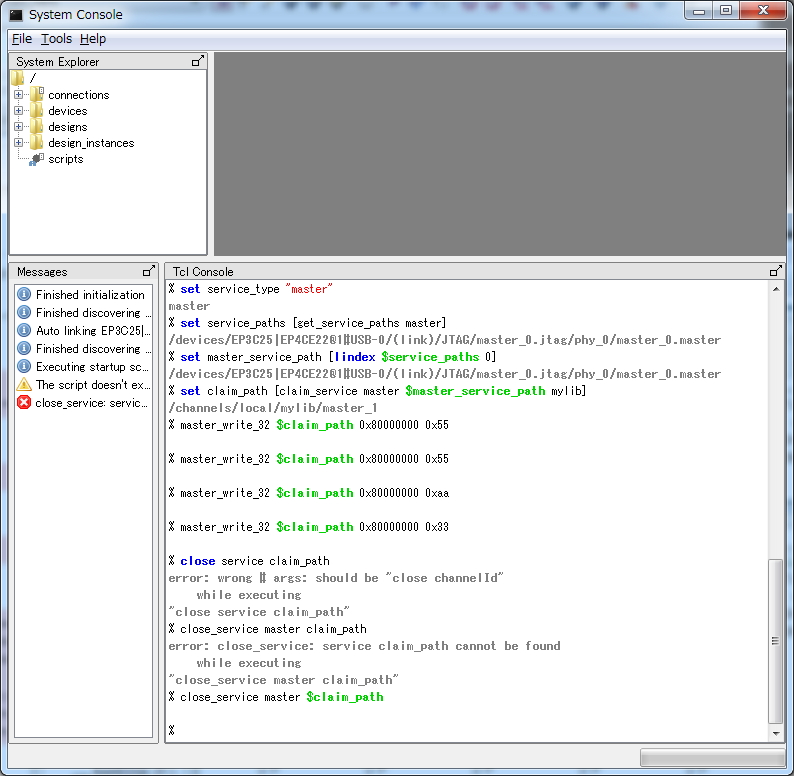

書き込み完了すれば早速テストを行ってみます。Tools -> System Debugging Tools -> System Console メニューを選択してシステムコンソールを起動します。ALTERA の オンライン資料: Quartus II 開発ソフトウェア に Analyzing and Debugging Designs with System Console という pdf があり、これにコマンド説明があります。

% set master_path [lindex [get_service_paths master] 0] /devices/EP3C25|EP4CE22@1#USB-0/(link)/JTAG/master_0.jtag/phy_0/master_0.master % open_service master $master_path % master_write_32 $master_path 0x80000000 0x55

という方法も動きますが、先程の PDF では open_service はサポートされなくなり claim_service を使ってとありますので注意必要です。

% set service_paths [get_service_paths master] /devices/EP3C25|EP4CE22@1#USB-0/(link)/JTAG/master_0.jtag/phy_0/master_0.master % set master_service_path [lindex $service_paths 0] /devices/EP3C25|EP4CE22@1#USB-0/(link)/JTAG/master_0.jtag/phy_0/master_0.master % set claim_path [claim_service master $master_service_path mylib] /channels/local/mylib/master_1 % master_write_32 $claim_path 0x80000000 0x55 % master_write_32 $claim_path 0x80000000 0xaa % master_write_32 $claim_path 0x80000000 0x33 % close_service master $claim_path

ということで、claim_service 版で 0x8000_0000 に値を書き込みして LED の表示が変るかやってみます。

無事動いてよかったです。