FPGA に関することは、超有名 Blog を初めに、すんごいハードを作成されている方などが公開されている情報がたくさんあって、参考にさせていただいています。今日はたまたま ZYBO が目についたので、Vivado に慣れましょうと Digilent のサイトにあったサンプルプロジェクトを動かしてみることにしました。

Zybo Zynq-7000 ARM/FPGA SoC Trainer Board のページ内に、リソースセンターというのがあって、そこにある ZYBO HDMI Demo というやつです。

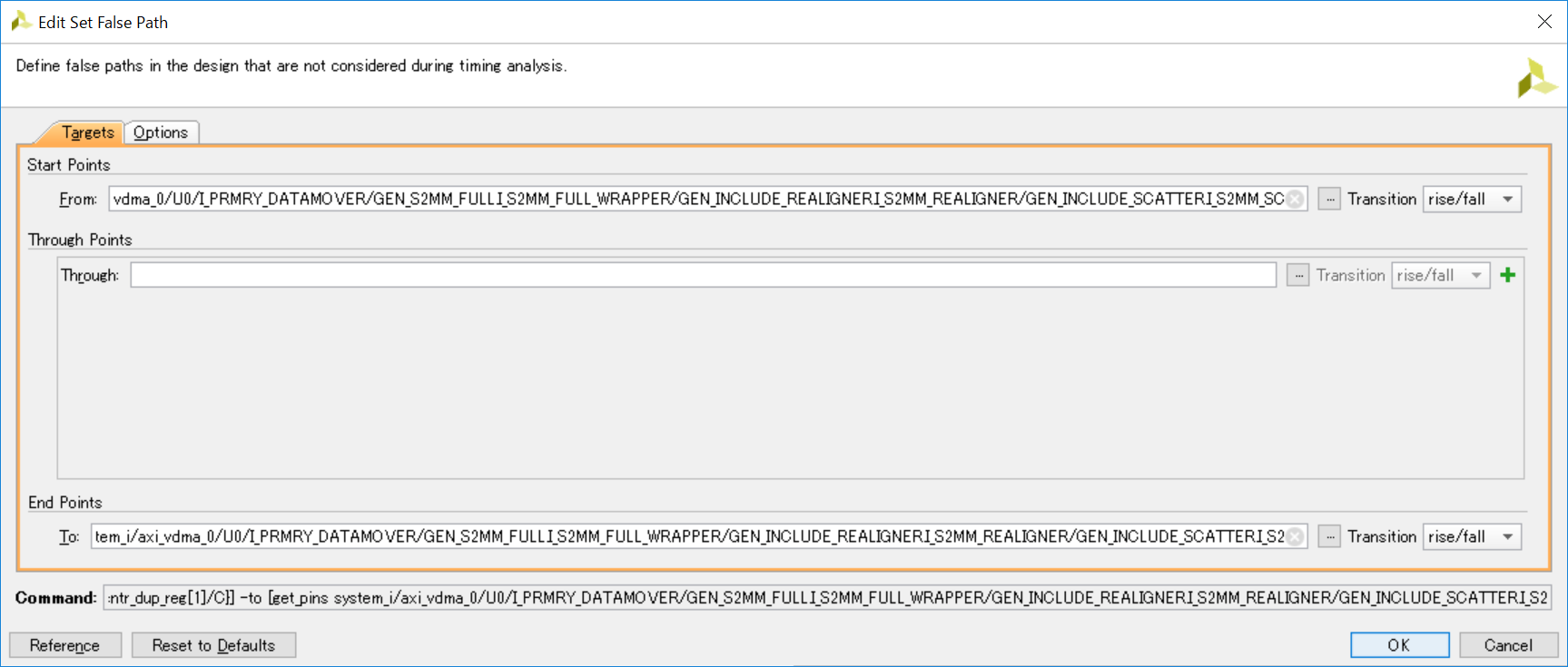

基本は、手順通り Vivado を起動してプロジェクトを作成。その後、Synthesis -> Implementation と進んみますが、サンプルプロジェクトは Vivado 2015.3 で、私の使用しているバージョンは 2015.4.1 とちょっと違います。最初に出たエラーはプロジェクト作成 TCL スクリプトでエラーが出て、プロジェクトの作成に失敗しました。これは、TCLスクリプトに記述されていたバージョン番号を直接書き換えて、プロジェクト作成からやり直しました。次に Implementation でタイミングエラーが発生しました。Report Timing Summary を表示させて、タイミングエラーを確認。

タイミングエラーを無視するよう false path 設定して、Synthesis -> Implementation -> Generate bit stream まで行けました。これで FPGA 側は OK です。

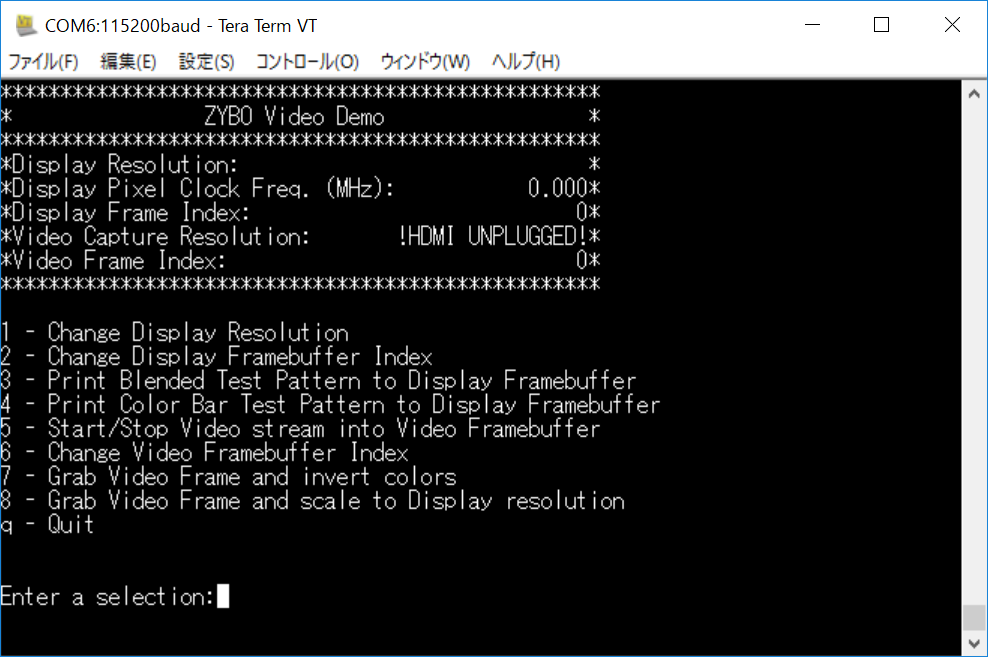

次に、SDK を起動して、ソフトの Build を行います。こちらは問題なく Build されました。SDK から bitstream とソフト ZYBO に書き込めば動き出します。Tera Term で COM ポート接続するとあ↓のようなメニューが表示されます。

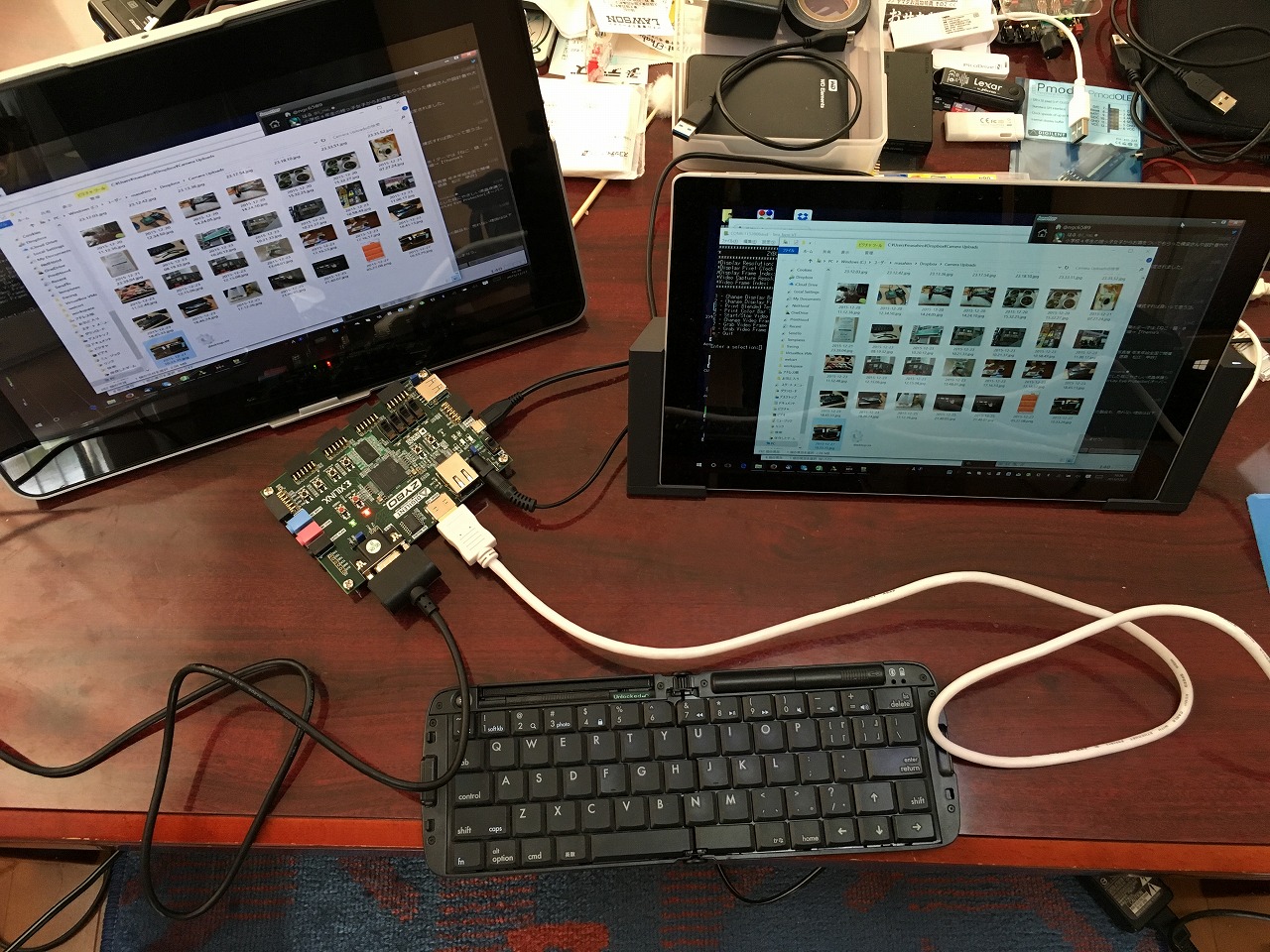

VGA 端子に液晶モニタ、HDMI には PC の出力を接続してみたところ、変換されて出力出来ました。

ビデオカメラの出力では、信号を認識出来ませんでした。