普段 DWMとか読まないんで、CPLDやFPGAの事情はさっぱりわかりません。昔のページに XILINX XC9500シリーズの

CPLD使った記事も書きましたが2002年6月のことで、当然ここのサイトには掲載してません。

今更という感じはあるのですが、久しぶりにやってみたくなったので入門キットを買ってボチボチ遊びたいと思います。

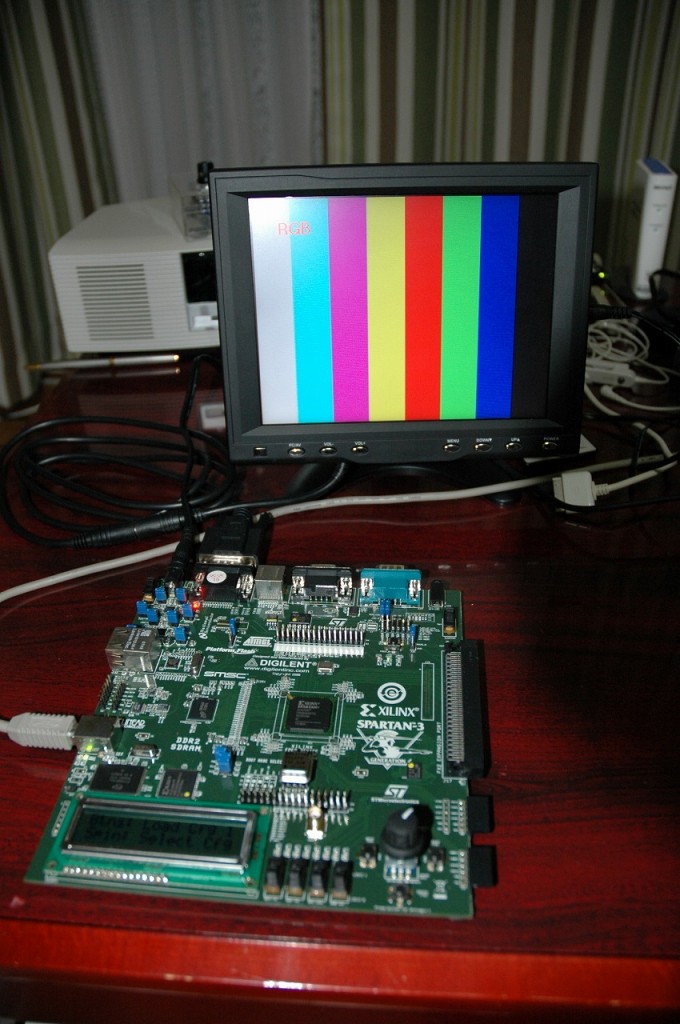

FPGAの「Hello, World」は、はやり LEDピコピコですが、今回は飛ばして VGA 出力の練習です。

Verilog HDL入門本見ながら書いてみました。以下ソースとUCFです。

Webpack 10.1で作成してとりあえず成功っと

モニタはPCデポ店頭に積んであったセリング KW-M80C というとこのSVGAモニタでアナログRGBとコンポッジト入力だけの

シンプル構成です。1万4千円くらいだったと思います。まぁちょっと使う程度なら使えるモニタです。

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 12:46:33 06/22/2008 // Design Name: // Module Name: vga // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// // // -- 水平タイミング -- // 表示期間: 640ドット // フロントポーチ: 16ドット // 水平同期: 96ドット(656) // バックポーチ: 48ドット(752) // // -- 垂直タイミング -- // 表示期間: 480ライン // フロントポーチ: 10ライン // 垂直同期: 2ライン(490) // バックポーチ: 29ライン(492) module vga(CLK_50MHZ, VGA_R, VGA_G, VGA_B, VGA_HSYNC, VGA_VSYNC); input CLK_50MHZ; output [3:0] VGA_R; output [3:0] VGA_G; output [3:0] VGA_B; output VGA_HSYNC; output VGA_VSYNC; reg [3:0] VGA_R; reg [3:0] VGA_G; reg [3:0] VGA_B; reg VGA_HSYNC; reg VGA_VSYNC; wire clk_25mhz; reg clk_25mhz_a; assign clk_25mhz = clk_25mhz_a; reg [9:0] hcount; reg [9:0] vcount; /* 25MHz のクロック作成 */ always @(posedge CLK_50MHZ) begin clk_25mhz_a <= ‾clk_25mhz_a; end /* 25Mhz のクロックで画面描画 */ always @(posedge clk_25mhz) begin // 水平タイミング hcount <= hcount + 1; // 水平カウント 800 で一周 if(hcount > 10'd799) begin hcount <= 0; vcount <= vcount + 1; end // 水平同期出力 if(hcount == 10'd655) begin VGA_HSYNC <= 0; VGA_R <= 4'b0000; VGA_G <= 4'b0000; VGA_B <= 4'b0000; end // 水平同期出力終了 if(hcount == 10'd751) begin VGA_HSYNC <= 1; end // 垂直タイミング // 521 ラインで一周 if(vcount > 10'd520) begin vcount <= 0; end // 垂直同期開始 if(vcount == 10'd489) begin VGA_VSYNC <= 0; end // 垂直同期終了 if(vcount == 10'd491) begin VGA_VSYNC <= 1; end // カラーバーもどき → メモリインタフェースにする if(hcount == 10'd0) begin VGA_R <= 4'b1111; VGA_G <= 4'b1111; VGA_B <= 4'b1111; end if(hcount == 10'd79) begin VGA_R <= 4'b0000; VGA_G <= 4'b1111; VGA_B <= 4'b1111; end if(hcount == 10'd159) begin VGA_R <= 4'b1111; VGA_G <= 4'b0000; VGA_B <= 4'b1111; end if(hcount == 10'd239) begin VGA_R <= 4'b1111; VGA_G <= 4'b1111; VGA_B <= 4'b0000; end if(hcount == 10'd319) begin VGA_R <= 4'b1111; VGA_G <= 4'b0000; VGA_B <= 4'b0000; end if(hcount == 10'd399) begin VGA_R <= 4'b0000; VGA_G <= 4'b1111; VGA_B <= 4'b0000; end if(hcount == 10'd479) begin VGA_R <= 4'b0000; VGA_G <= 4'b0000; VGA_B <= 4'b1111; end if(hcount == 10'd559) begin VGA_R <= 4'b0000; VGA_G <= 4'b0000; VGA_B <= 4'b0000; end end endmodule <pre><code> NET "VGA_R<3>" LOC = "C8" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_R<2>" LOC = "B8" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_R<1>" LOC = "B3" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_R<0>" LOC = "A3" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_G<3>" LOC = "D6" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_G<2>" LOC = "C6" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_G<1>" LOC = "D5" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_G<0>" LOC = "C5" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_B<3>" LOC = "C9" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_B<2>" LOC = "B9" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_B<1>" LOC = "D7" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_B<0>" LOC = "C7" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_HSYNC" LOC = "C11" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_VSYNC" LOC = "B11" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "CLK_50MHZ" LOC = "E12"| IOSTANDARD = LVCMOS33 ; # NET "CLK_AUX" LOC = "V12"| IOSTANDARD = LVCMOS33 ; # NET "CLK_SMA" LOC = "U12"| IOSTANDARD = LVCMOS33 ;